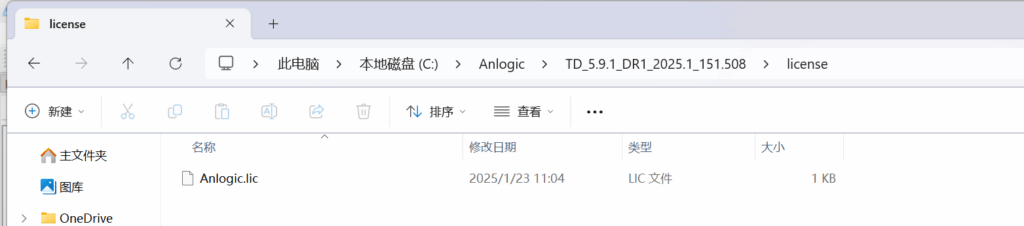

创建工程之前确定先获取到License,放到对应目录,国货东西License获取方法这里没法多说.

开始创建工程.

根据器件选择

创建源码文件

在这里约束IO

做过FPGA都知道Syn和Phy的区别,分别在合适阶段做就行.

正常下载

PL开发其实和其他FPGA差别不大,不过既然是SOC,当然能要讲PS-PL开发.

进Tools-Design Integrator

创建设计.

我很懒,所以保持原有名字.

添加处理器核心

像不像Xilinx风格.

双击IP核进设置.

开启DDR,因为会在DDR运行,暂时不调参数(主要是我不知道)

配置外设,打开UART 1

确认后超长等待.

这里暂时先不写PL端,先把PL的AXI ACLK和PL参考时钟短接起来,双击端口进入连线模式.

然后退出,提示生成,按提示去生成.之后工程里看到一堆文件.

然后查看到这个,应该是因为只用PS不用导出端口.

新建一个顶层,简单实例化一下.

结果报告是空盒,所以还不行.于是写一个简单LED.

module top(

output wire led

);

assign led = 1'b1;

design_0 design_0_inst(

);

endmodule

这下是不报告空壳了,但是IO约束向导打不开?

找了好久没办法,似乎点重新RUN,结束后会弹出一个提示,10秒点内OK,之后才可以编辑引脚,很奇怪的逻辑.如果你忘了点,你花了几分钟的综合就白费了.这综合如果大工程得几十分钟你想想.

然后依次Syn->Phy,直接点Phy他都知道Syn Out of date了,他自己都不会调用.

导出HPF文件.

导出

现在用到另一个工具FD.

安装后似乎就有一定的使用时间.

新建一个Platform Project.

选中刚才创建的HPF.

然后创建APP

第一个是fsbl并且名字必须也是fsbl.

创建后编译一下,没有al_spi_nor.h,是几个意思啊.

折腾了好久,找到了办法,我到安装目录找到这个文件

C:\Anlogic\FD_2025.1_SP1\data\embeddedsw\dr1x90\fpsoc\driver\ps_driver\spi-nor

复制过来,这里还有一点,要把Platform工程改名bsp,不然fsbl一样不行.

别看还打叉,其实已经可以了.

调试试试

应该算成功的.

一波三折呢.

后续其他再看,其实有用过Xilinx SOC的大概率已经知道接下来怎么做了.