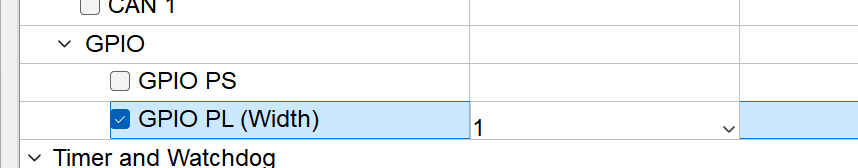

在上一期的工程之后,添加一个EMIO(GPIO PL)

然后三路都手动引出.

然后写一个简单的顶层.

module top(

inout led

);

wire pl_gpio_in;

wire pl_gpio_out;

wire pl_gpio_oe;

assign led = pl_gpio_oe ? pl_gpio_out : 1'bz;

assign pl_gpio_in = 1'b0;

design_0 design_0_inst(

.pl_gpio_in(pl_gpio_in),

.pl_gpio_out(pl_gpio_out),

.pl_gpio_oe(pl_gpio_oe)

);

endmodule

然后到PS,资料相当零碎,还是看头文件自己研究.

摸索了一下,54就是EMIO0,并没有方向设置什么的.

#include <stdio.h>

#include <math.h>

#include <time.h>

#include "al_core.h"

#include <stdlib.h>

#include "al_gpio_hal.h"

AL_S32 main()

{

AL_GPIO_HalStruct *GPIO;

const AL_CHAR *str = "Hello World From Anlogic!";

printf("%s \r\n""BSP version:%d-%d-%d\r\n", str, AL_BSP_VERSION_MAJOR, AL_BSP_VERSION_MINOR, AL_BSP_VERSION_PATCH);

printf(" __ __ ____ _ ______ __ __ \r\n");

printf(" / / / /_ / / /___ | | / / __ \\_____/ ____/ / \r\n");

printf(" / /_/ / _ \\/ / / __ \\ | | /| / / / / / ___/ / __ / \r\n");

printf(" / __ / __/ / / /_/ / | |/ |/ / /_/ / / / / /_/ / \r\n");

printf("/_/ /_/\\___/_/_/\\____/ |__/|__/\\____/_/ /_/\\__ _/ \r\n");

AL_S32 ret = AlGpio_Hal_Init(&GPIO, 0, AL_NULL);

for(;;){

AlGpio_Hal_WritePin(GPIO,54,0);

AlSys_MDelay(2000);

AlGpio_Hal_WritePin(GPIO,54,1);

AlSys_MDelay(2000);

}

return 0;

}

下载时候默认不下载bit,所以调试设置记得做.

内容虽短,但是这次踩坑比较多,花了太多时间了.

接下来简单说一下固化.

三个都设置为sha2 + fsbl

选一个路径然后点下面的创建.

我猜下一步编程,,我实测X4我的板子不行,只能换X1,离开JTAG重新上电可以运行.

日志

[BOOT INFO] Boot Reg value : 0x00000001

[BOOT INFO] Boot Mode : QSPI 24 bit Boot Mode

[BOOT INFO] IDE_VERSION : Release: 5.9.1 Build: 151508

[BOOT INFO] Bitstream Export Time: 2025/ 9/21 13:47

[BOOT INFO] HPF_EXPORT_TIME : 2025/09/21 13:48:09

[BOOT INFO] Compile Time : Sep 21 2025 13:50:08

[BOOT INFO] HPF Version : 202501

[DDR INFO] DRAM 256M x16, Use DQ[31:0]

[DDR INFO] Available Capacity 1024 MB

[DDR FW] Version 4.2

[DDR FW] Compile Time: Mar 28 2025 15:28:37

[DDR GPLL] fck = 533.280 MHz, fbk_div = 64, out_div = 2

[DDR GPLL] gmc = 0 icp = 10 lpf_cap = 2 lpf_res = 4 kvco = 0

[DDR Vref] Internal 0x10

[DDR PPC] Enable Lane Mask = 0xF

[DDR MDL] DX0 = 0x12c012c 6.254 ps

[DDR MDL] DX1 = 0x12d012d 6.233 ps

[DDR MDL] DX2 = 0x12e012e 6.212 ps

[DDR MDL] DX3 = 0x12e012e 6.212 ps

[FAST INIT] MDL = 299 301 302 301

[DDR MRS] DDR3 Mode

[DDR MRS] MR0 = 0x940

[DDR MRS] MR1 = 0x4

[DDR MRS] MR2 = 0x8

[DDR MRS] MR3 = 0x0

[DDR GATE] DX0GSR0.GDQSPRD = 148

[DDR GATE] Done

[DDR WLADJ] Done

[DDR TRAIN #0] RDEYE:O WREYE:O

========================================

DX DGSL WLSL WLD WDQD DQSGD RDQSD RDQSND

----------------------------------------

0 2 2 0 66 146 72 61

1 3 2 0 67 0 74 61

2 3 2 0 65 6 76 64

3 2 2 1 68 147 76 63

========================================

==================== In Stage 1 ====================

System reset

PMU Error Config Init

PMU Error Config Init

history reset reason: 00000000

history pmu status 0: 00000000

history pmu status 1: 00000000

------------------AXI-MONITOR------------------

debug timeout flag: [4:0] - aw, w, b, ar, r

ddr_s0 : 0x0

ddr_s1 : 0x0

ddr_s2 : 0x0

ddr_s3 : 0x0

sx2x_m0 : 0x0

sx2x_m1 : 0x0

ocm_s2 : 0x0

sh_m2 : 0x0

smc : 0x0

dmacx : 0x0

gp_s0 : 0x0

gp_s1 : 0x0

hp_s0 : 0x0

hp_s1 : 0x0

apu : 0x0

jpu : 0x0

main_s6 : 0x0

main_m6 : 0x0

main_s1 : 0x0

main_m0 : 0x0

acp : 0x0

-----------------------------------------------

mark fsbl is running...

==================== In Stage 2 ====================

Boot Mode: 0x00000001

QSPI 24/32 Boot Mode

Flash model: GD25LB256E

Flash is in x4 mode

FsblInstancePtr->ImageOffsetAddress: 0x0

boot header copy finished...

Calculated Checksum: 0x3FC29918

checksum check pass...

partition headers copy finished...

image header authentication not enabled....

qspi width sel : 0x00000000

image id : 0x43474C41

enc status : 0x00000000

bh attribute : 0x00000000

bh ac offset : 0x00000000

first parti hdr offset: 0x00000300

partition num : 0x00000003

bh checksum : 0x3FC29918

PartitionNum: 3

==================== In Stage 3 ====================

wdt restart

Partition Header Checksum: 0xC9B85AB2

Calculated Checksum: 0xC9B85AB2

checksum check pass...

Hash Type: 0x00000800

Hash SHA256.

Auth Type : 0

Efuse Auth Type : 0

Authentication NOT enabled...

Enc Type : 0

Efuse Enc Type : 0

Encrypt NOT enabled.

destination cpu: 0x00000020

destination dev: 0x00000080

check partition length:

Partition Header Infomation:

Partition Length : 0x002BEC40

Extracted Partition Length : 0x002BEC08

Total Partition Length : 0x002BEC80

Next Partition Header Offset: 0x00000380

Dest Execution Address : 0xFFFFFFFF

Dest Load Address : 0x0

Partition Offset : 0x00030A40

Partition Attribute : 0x000008A0

Hash Data offset : 0x002EF680

AC Offset : 0x00000000

Partition Header Checksum : 0xC9B85AB2

loading pl partition...

PCAP RESET

Re-enable PCAP

Boot device block size max: 4000

PL init done

cfg state: 00000001

Auth type : 00

Hash type : 02

Enc type : 65

Enc mode : 00

Key mode : 6E

to ddr in a whole block, then to pcap

partition src address : 0x00030A40

partition load dest address: 0x00100000

partition length : 0x002BEC40

whole block

calculate hash

read hash

Hash check passed...

cfg state before progdone: 00000007

==================== In Stage 3 ====================

wdt restart

Partition Header Checksum: 0xE9C1B103

Calculated Checksum: 0xE9C1B103

checksum check pass...

Hash Type: 0x00000800

Hash SHA256.

Auth Type : 0

Efuse Auth Type : 0

Authentication NOT enabled...

Enc Type : 0

Efuse Enc Type : 0

Encrypt NOT enabled.

destination cpu: 0x00000020

destination dev: 0x00000000

check partition length:

Partition Header Infomation:

Partition Length : 0x0001CC00

Extracted Partition Length : 0x0001CBF8

Total Partition Length : 0x0001CC40

Next Partition Header Offset: 0x00000000

Dest Execution Address : 0x8000000

Dest Load Address : 0x8000000

Partition Offset : 0x002EF6C0

Partition Attribute : 0x00000820

Hash Data offset : 0x0030C2C0

AC Offset : 0x00000000

Partition Header Checksum : 0xE9C1B103

loading ps partition...

partition src address : 0x2EF6C0

partition load dest address: 0x8000000

partition length : 0x0001CC00

Auth type : 00

Hash type : 02

Enc type : 65

Enc mode : 00

Key mode : 6E

calculate hash

Hash check passed...

ps partition copy finished

Update handoff values

==================== In Stage 4 ====================

Mark FSBL is completed...

wdt disable

Hello World From Anlogic!

BSP version:2025-1-1

__ __ ____ _ ______ __ __

/ / / /_ / / /___ | | / / __ \_____/ ____/ /

/ /_/ / _ \/ / / __ \ | | /| / / / / / ___/ / __ /

/ __ / __/ / / /_/ / | |/ |/ / /_/ / / / / /_/ /

/_/ /_/\___/_/_/\____/ |__/|__/\____/_/ /_/\__ _/