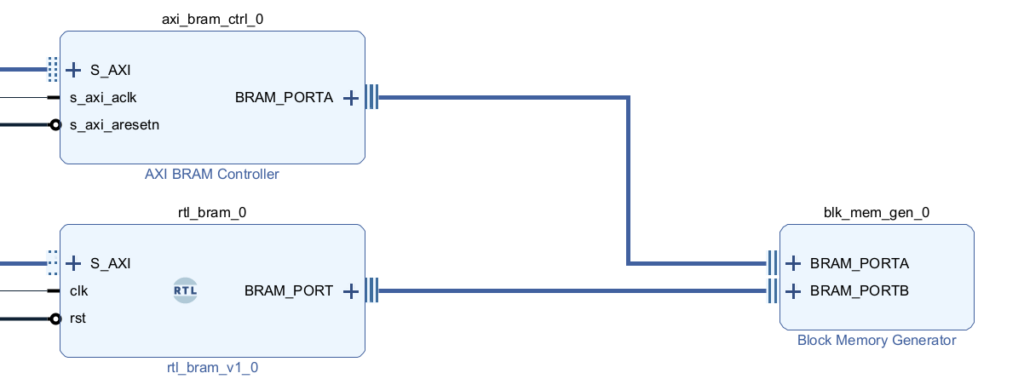

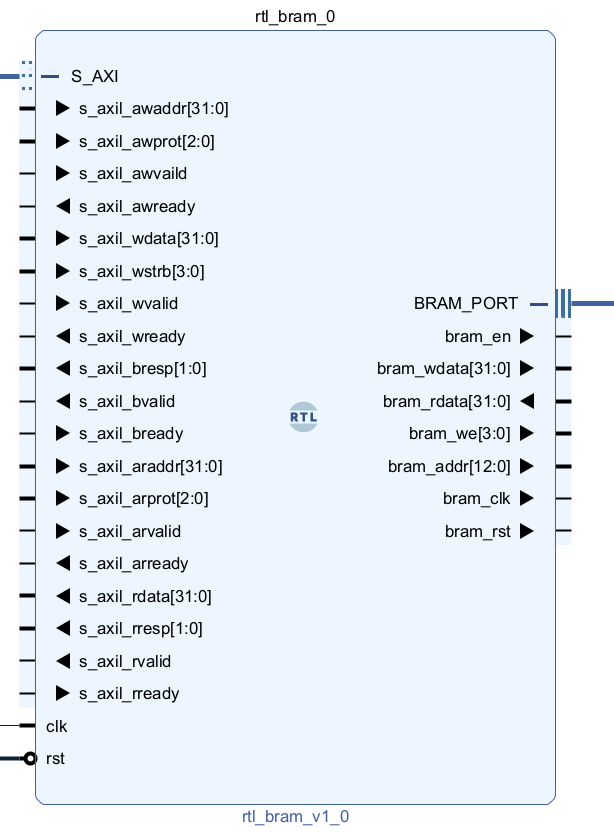

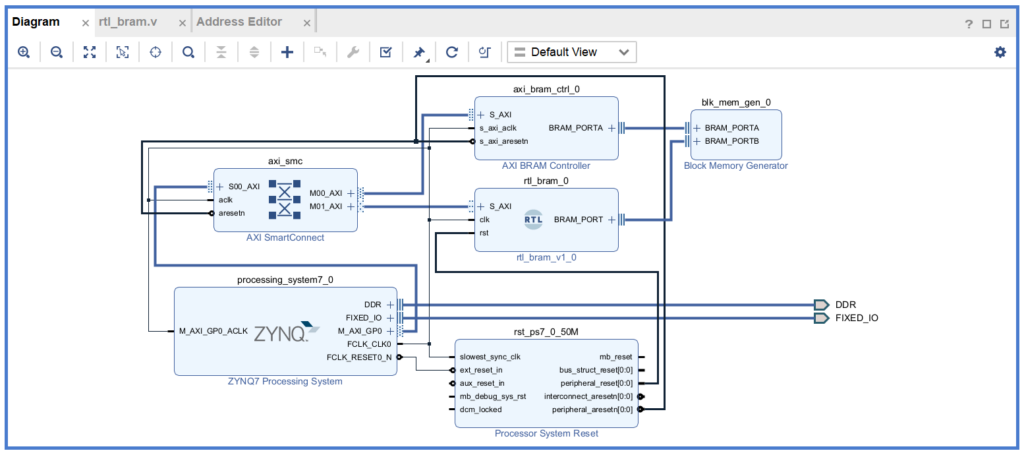

一般来说,我们的IP都会长得像上面的那样,定义好接口,像AXI这些直接连过去就完成了.

但是如果是RTL,默认是不会这样组合起端口的,这时候只要使用合适的原语就可以了.

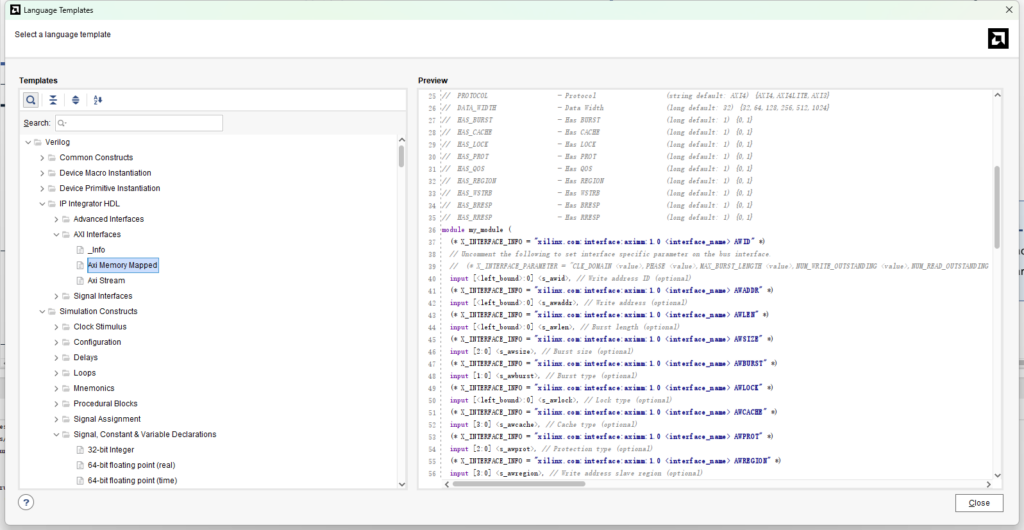

原语模板位置 Verilog -> IP Integrator HDL -> XXX,比如我这个是AXI,他就专门分类到AXI Interfaces里了.

然后在代码中给每个接口修饰.

(* X_INTERFACE_INFO = "xilinx.com:interface:aximm:1.0 S_AXI AWADDR" *)

input wire [31:0] s_axil_awaddr,

(* X_INTERFACE_INFO = "xilinx.com:interface:aximm:1.0 S_AXI AWPROT" *)

input wire [2:0] s_axil_awprot,

(* X_INTERFACE_INFO = "xilinx.com:interface:aximm:1.0 S_AXI AWVALID" *)

input wire s_axil_awvaild,

(* X_INTERFACE_INFO = "xilinx.com:interface:aximm:1.0 S_AXI AWREADY" *)

output wire s_axil_awready,

(* X_INTERFACE_INFO = "xilinx.com:interface:aximm:1.0 S_AXI WDATA" *)

input wire [31:0] s_axil_wdata,

(* X_INTERFACE_INFO = "xilinx.com:interface:aximm:1.0 S_AXI WSTRB" *)

input wire [3:0] s_axil_wstrb,

(* X_INTERFACE_INFO = "xilinx.com:interface:aximm:1.0 S_AXI WVALID" *)

input wire s_axil_wvalid,

(* X_INTERFACE_INFO = "xilinx.com:interface:aximm:1.0 S_AXI WREADY" *)

output wire s_axil_wready,

(* X_INTERFACE_INFO = "xilinx.com:interface:aximm:1.0 S_AXI BRESP" *)

output wire [1:0] s_axil_bresp,

(* X_INTERFACE_INFO = "xilinx.com:interface:aximm:1.0 S_AXI BVALID" *)

output wire s_axil_bvalid,

(* X_INTERFACE_INFO = "xilinx.com:interface:aximm:1.0 S_AXI BREADY" *)

input wire s_axil_bready,

(* X_INTERFACE_INFO = "xilinx.com:interface:aximm:1.0 S_AXI ARADDR" *)

input wire [31:0] s_axil_araddr,

(* X_INTERFACE_INFO = "xilinx.com:interface:aximm:1.0 S_AXI ARPROT" *)

input wire [2:0] s_axil_arprot,

(* X_INTERFACE_INFO = "xilinx.com:interface:aximm:1.0 S_AXI ARVALID" *)

input wire s_axil_arvalid,

(* X_INTERFACE_INFO = "xilinx.com:interface:aximm:1.0 S_AXI ARREADY" *)

output wire s_axil_arready,

(* X_INTERFACE_INFO = "xilinx.com:interface:aximm:1.0 S_AXI RDATA" *)

output wire [31:0] s_axil_rdata,

(* X_INTERFACE_INFO = "xilinx.com:interface:aximm:1.0 S_AXI RRESP" *)

output wire [1:0] s_axil_rresp,

(* X_INTERFACE_INFO = "xilinx.com:interface:aximm:1.0 S_AXI RVALID" *)

output wire s_axil_rvalid,

(* X_INTERFACE_INFO = "xilinx.com:interface:aximm:1.0 S_AXI RREADY" *)

input wire s_axil_rready,这样我们就把AXI接口定义了,同样的,我们可以到另外找到BRAM的原语也修饰一下.

(* X_INTERFACE_PARAMETER = "FREQ_HZ 1000000" *)

(* X_INTERFACE_INFO = "xilinx.com:interface:bram:1.0 BRAM_PORT CLK" *)

output wire bram_clk,

(* X_INTERFACE_INFO = "xilinx.com:interface:bram:1.0 BRAM_PORT EN" *)

(* X_INTERFACE_PARAMETER = "MASTER_TYPE BRAM_CTRL,RITE_MODE READ_WRITE" *)

output wire bram_en,

(* X_INTERFACE_INFO = "xilinx.com:interface:bram:1.0 BRAM_PORT WE" *)

output wire [3:0] bram_we,

(* X_INTERFACE_INFO = "xilinx.com:interface:bram:1.0 BRAM_PORT RST" *)

output wire bram_rst,

(* X_INTERFACE_INFO = "xilinx.com:interface:bram:1.0 BRAM_PORT DOUT" *)

input wire [31:0] bram_rdata,

(* X_INTERFACE_INFO = "xilinx.com:interface:bram:1.0 BRAM_PORT DIN" *)

output wire [31:0] bram_wdata,

(* X_INTERFACE_INFO = "xilinx.com:interface:bram:1.0 BRAM_PORT ADDR" *)

output wire [12:0] bram_addr最后就是得到我一开始图上的效果,模块展开图.

通过验证也没问题.

完整代码参考:https://gist.github.com/nickfox-taterli/5d76e80288d762bcf4631231d5389e22

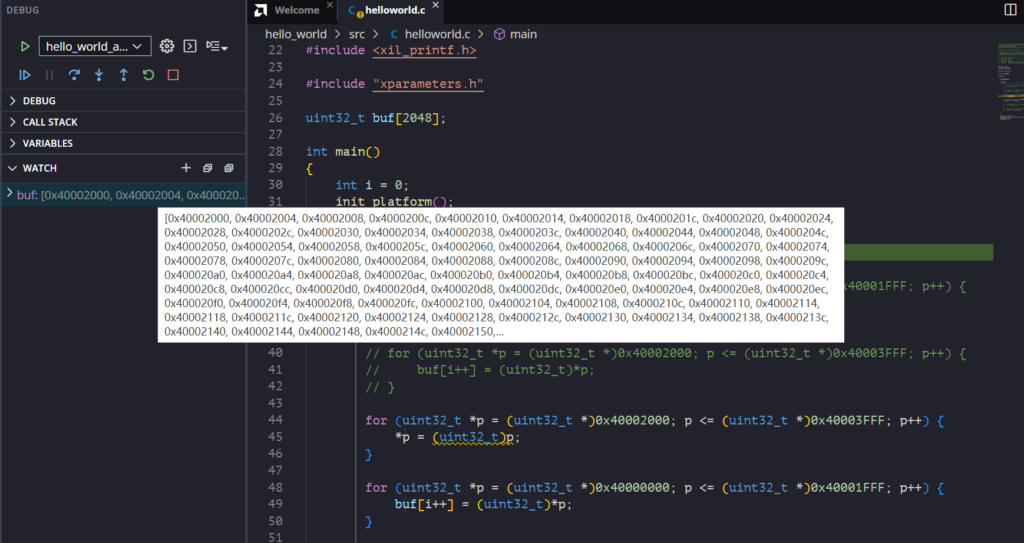

读写测试框架.

测试都没问题.