首先把项目递归克隆下来.

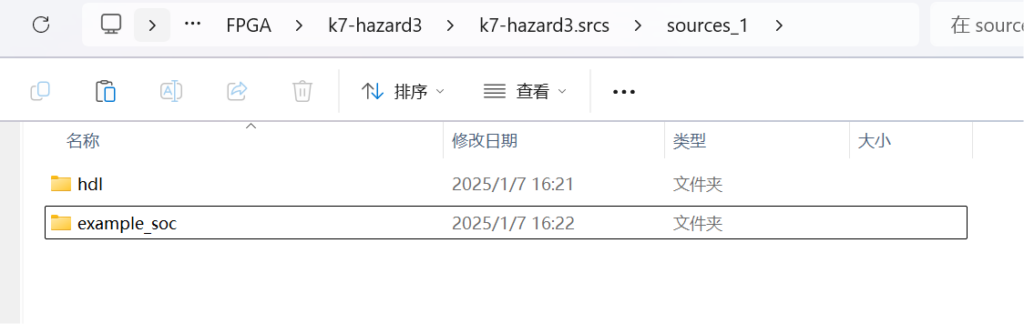

git clone --recursive https://github.com/Wren6991/Hazard3.git hazard3因为部分引用在libfpga里,如果不递归克隆,部分内容是找不到的,把HDL和example_soc复制到源码目录里.

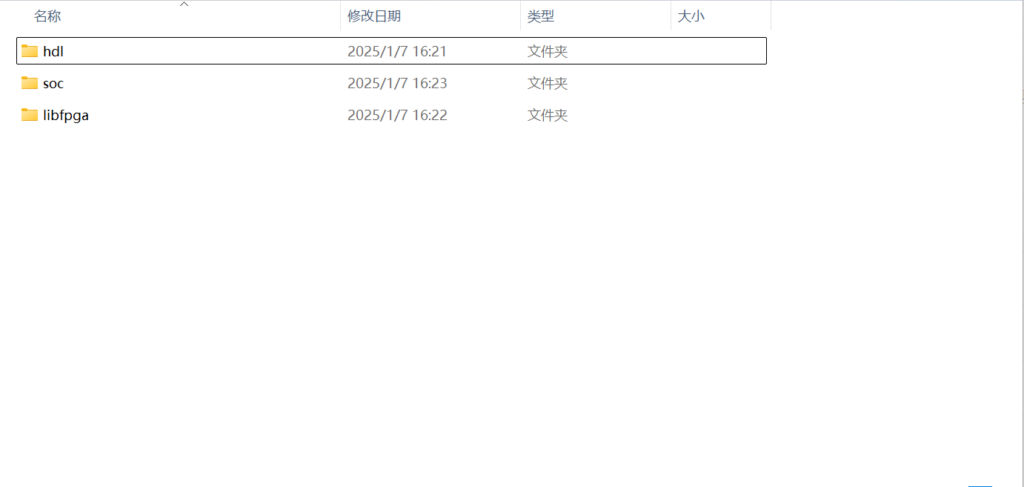

整个工程的所有.f文件就丢了,example_soc里也不是什么都要,否则影响递归导入,只保留libfpga和soc文件夹,并移动出来.

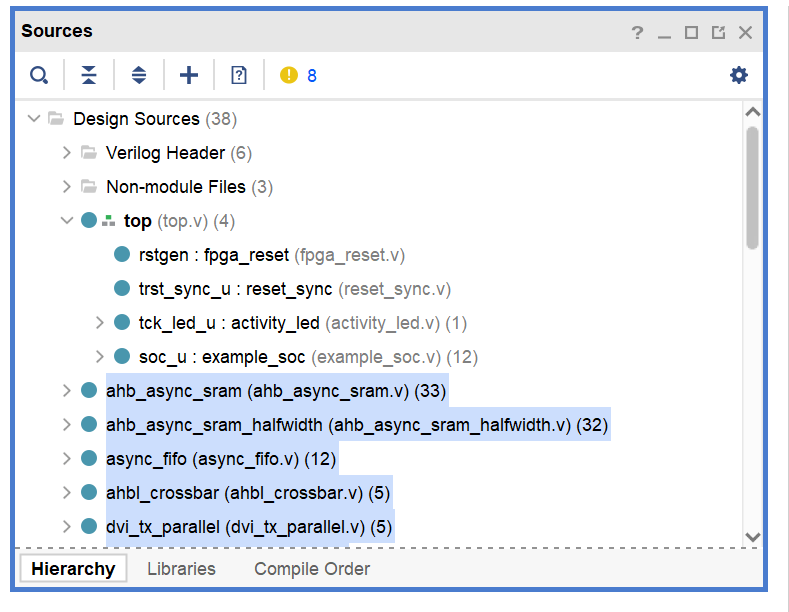

导入后还差顶层文件,建立例化一下.

module top (

input wire clk_osc,

input wire tck,

input wire tms,

input wire tdi,

output wire tdo,

output wire led,

output wire uart_tx,

input wire uart_rx

);

wire clk_sys = clk_osc;

wire rst_n_sys;

wire trst_n;

fpga_reset #(

.SHIFT (3)

) rstgen (

.clk (clk_sys),

.force_rst_n (1'b1),

.rst_n (rst_n_sys)

);

reset_sync trst_sync_u (

.clk (tck),

.rst_n_in (rst_n_sys),

.rst_n_out (trst_n)

);

activity_led #(

.WIDTH (1 << 8),

.ACTIVE_LEVEL (1'b0)

) tck_led_u (

.clk (clk_sys),

.rst_n (rst_n_sys),

.i (tck),

.o (led)

);

example_soc #(

.CLK_MHZ (50),

.EXTENSION_A (1),

.EXTENSION_C (0),

.EXTENSION_M (1),

.EXTENSION_ZBA (0),

.EXTENSION_ZBB (0),

.EXTENSION_ZBC (0),

.EXTENSION_ZBS (0),

.EXTENSION_ZBKB (0),

.EXTENSION_ZIFENCEI (0),

.EXTENSION_XH3BEXTM (0),

.EXTENSION_XH3PMPM (0),

.EXTENSION_XH3POWER (0),

.CSR_COUNTER (0),

.U_MODE (0),

.PMP_REGIONS (0),

.BREAKPOINT_TRIGGERS (0),

.IRQ_PRIORITY_BITS (0),

.REDUCED_BYPASS (0),

.MULDIV_UNROLL (1),

.MUL_FAST (0),

.MUL_FASTER (0),

.MULH_FAST (0),

.FAST_BRANCHCMP (1),

.BRANCH_PREDICTOR (0)

) soc_u (

.clk (clk_sys),

.rst_n (rst_n_sys),

.tck (tck),

.trst_n (trst_n),

.tms (tms),

.tdi (tdi),

.tdo (tdo),

.uart_tx (uart_tx),

.uart_rx (uart_rx)

);

endmodule等识别模块结构后,把未用到的丢掉,因为这个项目其实是一个SOC,还包含着外设呢,当然还有tb文件刚才也连带不小心导入了.

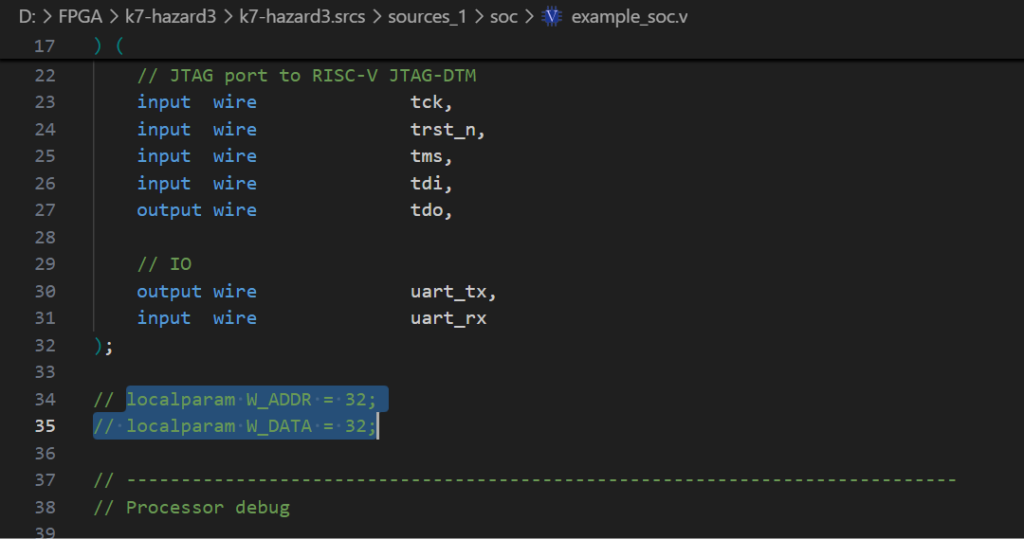

example_soc的WIDTH定义在config.vh已经写了,这里是多余,可以丢掉.

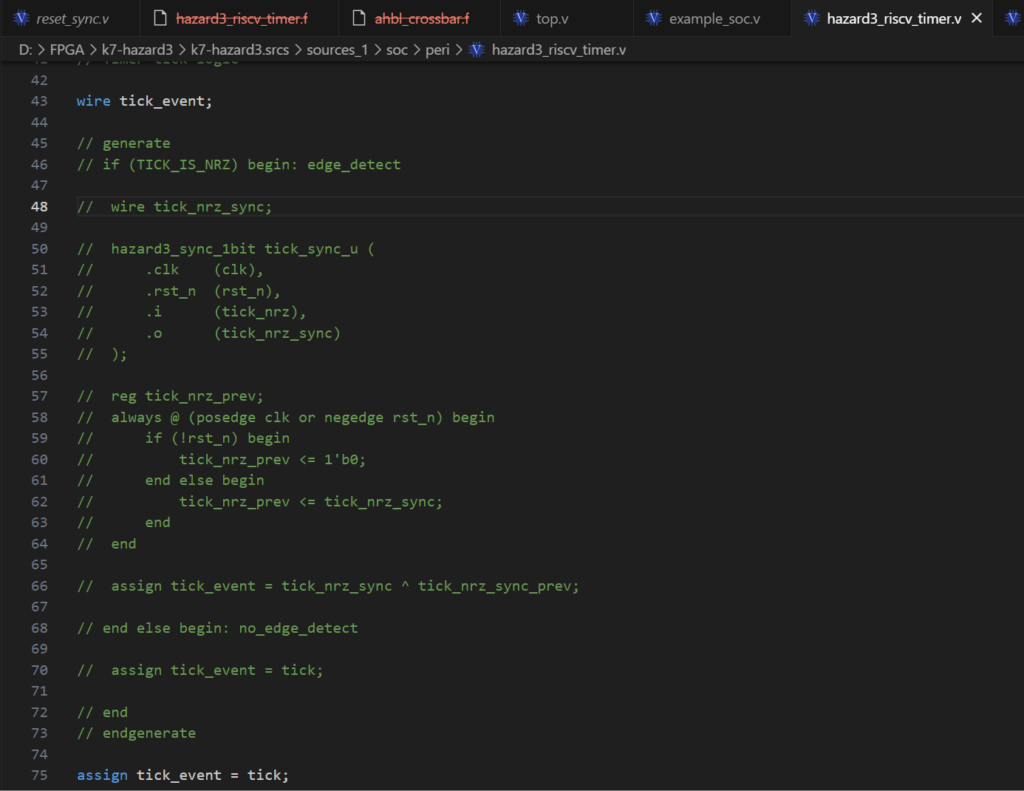

即使不综合这个分支,generate分支依然会被synth检查,所以直接注释掉.

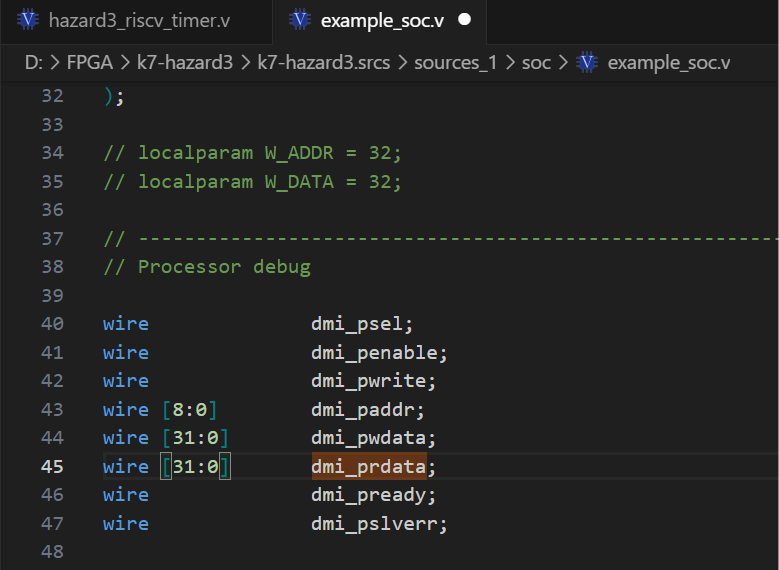

prdata是一个输出网络,应该定义为wire来链接.

解决两个问题后,synth应该就可以成功.

绑定引脚和时钟约束应该不用多说了.

set_property PACKAGE_PIN G22 [get_ports clk_osc]

set_property PACKAGE_PIN A23 [get_ports led]

set_property PACKAGE_PIN H12 [get_ports uart_rx]

set_property PACKAGE_PIN H14 [get_ports uart_tx]

set_property PACKAGE_PIN H11 [get_ports tms]

set_property PACKAGE_PIN F14 [get_ports tdo]

set_property PACKAGE_PIN G14 [get_ports tdi]

set_property PACKAGE_PIN F13 [get_ports tck]

set_property IOSTANDARD LVCMOS33 [get_ports clk_osc]

set_property IOSTANDARD LVCMOS33 [get_ports led]

set_property IOSTANDARD LVCMOS33 [get_ports tck]

set_property IOSTANDARD LVCMOS33 [get_ports tdi]

set_property IOSTANDARD LVCMOS33 [get_ports tdo]

set_property IOSTANDARD LVCMOS33 [get_ports tms]

set_property IOSTANDARD LVCMOS33 [get_ports uart_rx]

set_property IOSTANDARD LVCMOS33 [get_ports uart_tx]

set_property IS_CLOCK FALSE [get_ports tck]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets tck_IBUF]

create_clock -period 20.000 -name clk_osc -waveform {0.000 10.000} [get_ports clk_osc]

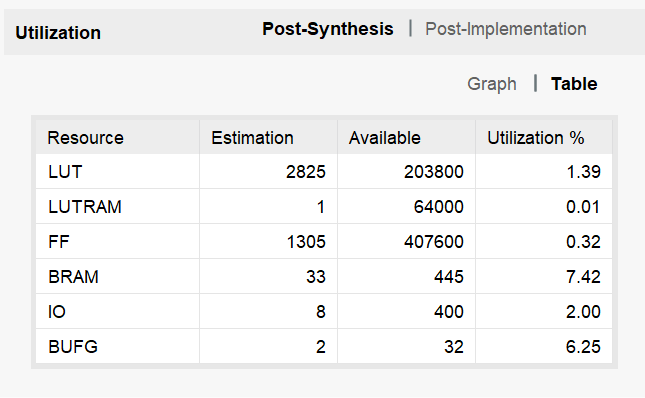

综合成功,下载到片上,测试找到内核.

openocd -f openocd.cfg

Open On-Chip Debugger 0.12.0+dev-gebec950-dirty (2024-09-27-16:29)

Licensed under GNU GPL v2

For bug reports, read

http://openocd.org/doc/doxygen/bugs.html

Warn : An adapter speed is not selected in the init scripts. OpenOCD will try to run the adapter at very low speed (100 kHz).

Warn : To remove this warnings and achieve reasonable communication speed with the target, set "adapter speed" or "jtag_rclk" in the init scripts.

Info : Using CMSIS-DAPv2 interface with VID:PID=0xd6e7:0x3507, serial=012345ABCDEF

Info : CMSIS-DAP: SWD supported

Info : CMSIS-DAP: JTAG supported

Info : CMSIS-DAP: Atomic commands supported

Info : CMSIS-DAP: Test domain timer supported

Info : CMSIS-DAP: FW Version = 2.1.0

Info : CMSIS-DAP: Interface Initialised (JTAG)

Info : SWCLK/TCK = 0 SWDIO/TMS = 0 TDI = 0 TDO = 0 nTRST = 0 nRESET = 0

Info : CMSIS-DAP: Interface ready

Info : clock speed 100 kHz

Info : cmsis-dap JTAG TLR_RESET

Info : cmsis-dap JTAG TLR_RESET

Info : JTAG tap: hazard3.cpu tap/device found: 0xdeadbeef (mfg: 0x777 (Fabric of Truth Inc), part: 0xeadb, ver: 0xd)

Info : [hazard3.cpu] datacount=1 progbufsize=2

Info : [hazard3.cpu] Disabling abstract command reads from CSRs.

Info : [hazard3.cpu] Disabling abstract command writes to CSRs.

Info : [hazard3.cpu] Examined RISC-V core

Info : [hazard3.cpu] XLEN=32, misa=0x40001101

Info : [hazard3.cpu] Examination succeed

Info : starting gdb server for hazard3.cpu on 3333

Info : Listening on port 3333 for gdb connections

hazard3.cpu halted due to debug-request.

Info : Listening on port 6666 for tcl connections

Info : Listening on port 4444 for telnet connections

调试配置文件.

adapter driver cmsis-dap

# remote_bitbang host localhost

# remote_bitbang port 9824

transport select jtag

set _CHIPNAME hazard3

jtag newtap $_CHIPNAME cpu -irlen 5

set _TARGETNAME $_CHIPNAME.cpu

target create $_TARGETNAME riscv -chain-position $_TARGETNAME

gdb_report_data_abort enable

init

halt

如果要想下载代码等,还要自行再实现一些其他功能,总线实现在hazard3_cpu_1port模块都有写,实际协议是AHB5,也可以换用IBUS,DBUS分离的那个CPU例化.

另外用这个核心的芯片RP2350实际是包含了很多外设的,以及BOOTROM也是软件实现的,这个在FPGA上综合的核心只能说是一个最小核心例子,并不是说他就是RP2350.

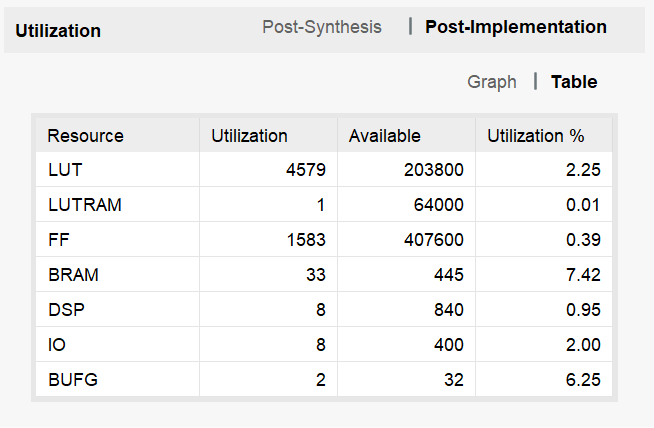

开启所有指令支持,分支预测等最终的综合消耗.