这个板子应该是某个学校的板子,偶然看到,对方说SFP没有定义资料,只有默认的XDC约束可以公开下载,这算什么事,自己找一遍就是.

写一个模块,分频时钟,不管他是什么玩意,都进来分频.

module sniff_refclk (

// 四对 GT 参考时钟直接进 IBUFDS_GTE2

input wire MGTREFCLK0_115_P, input wire MGTREFCLK0_115_N,

input wire MGTREFCLK1_115_P, input wire MGTREFCLK1_115_N,

input wire MGTREFCLK0_116_P, input wire MGTREFCLK0_116_N,

input wire MGTREFCLK1_116_P, input wire MGTREFCLK1_116_N,

// 四个观测 LED

output wire led_115_0,

output wire led_115_1,

output wire led_116_0,

output wire led_116_1

);

wire c115_0, c115_0_div2, c115_1, c115_1_div2;

wire c116_0, c116_0_div2, c116_1, c116_1_div2;

IBUFDS_GTE2 ibuf_115_0 (.I(MGTREFCLK0_115_P), .IB(MGTREFCLK0_115_N),

.CEB(1'b0), .O(c115_0), .ODIV2(c115_0_div2));

IBUFDS_GTE2 ibuf_115_1 (.I(MGTREFCLK1_115_P), .IB(MGTREFCLK1_115_N),

.CEB(1'b0), .O(c115_1), .ODIV2(c115_1_div2));

IBUFDS_GTE2 ibuf_116_0 (.I(MGTREFCLK0_116_P), .IB(MGTREFCLK0_116_N),

.CEB(1'b0), .O(c116_0), .ODIV2(c116_0_div2));

IBUFDS_GTE2 ibuf_116_1 (.I(MGTREFCLK1_116_P), .IB(MGTREFCLK1_116_N),

.CEB(1'b0), .O(c116_1), .ODIV2(c116_1_div2));

// 用 ODIV2 输出上 BUFG(更干净/更容易收敛)

wire k115_0, k115_1, k116_0, k116_1;

BUFG bufg115_0(.I(c115_0_div2), .O(k115_0));

BUFG bufg115_1(.I(c115_1_div2), .O(k115_1));

BUFG bufg116_0(.I(c116_0_div2), .O(k116_0));

BUFG bufg116_1(.I(c116_1_div2), .O(k116_1));

reg [27:0] div115_0 = 0, div115_1 = 0, div116_0 = 0, div116_1 = 0;

always @(posedge k115_0) div115_0 <= div115_0 + 1'b1;

always @(posedge k115_1) div115_1 <= div115_1 + 1'b1;

always @(posedge k116_0) div116_0 <= div116_0 + 1'b1;

always @(posedge k116_1) div116_1 <= div116_1 + 1'b1;

assign led_115_0 = div115_0[27];

assign led_115_1 = div115_1[27];

assign led_116_0 = div116_0[27];

assign led_116_1 = div116_1[27];

endmodule

然后加上约束

# LEDs

set_property IOSTANDARD LVCMOS33 [get_ports led_115_0]

set_property IOSTANDARD LVCMOS33 [get_ports led_115_1]

set_property IOSTANDARD LVCMOS33 [get_ports led_116_0]

set_property IOSTANDARD LVCMOS33 [get_ports led_116_1]

set_property PACKAGE_PIN AF24 [get_ports led_115_0]

set_property PACKAGE_PIN AE21 [get_ports led_115_1]

set_property PACKAGE_PIN Y22 [get_ports led_116_0]

set_property PACKAGE_PIN Y23 [get_ports led_116_1]

# QUAD_115 MGTREFCLK0

set_property PACKAGE_PIN H6 [get_ports MGTREFCLK0_115_P]

set_property PACKAGE_PIN H5 [get_ports MGTREFCLK0_115_N]

# QUAD_115 MGTREFCLK1

set_property PACKAGE_PIN K6 [get_ports MGTREFCLK1_115_P]

set_property PACKAGE_PIN K5 [get_ports MGTREFCLK1_115_N]

# QUAD_116 MGTREFCLK0

set_property PACKAGE_PIN D6 [get_ports MGTREFCLK0_116_P]

set_property PACKAGE_PIN D5 [get_ports MGTREFCLK0_116_N]

# QUAD_116 MGTREFCLK1

set_property PACKAGE_PIN F6 [get_ports MGTREFCLK1_116_P]

set_property PACKAGE_PIN F5 [get_ports MGTREFCLK1_116_N]

# 清掉可能误加在这些端口上的普通 IO 属性

reset_property IOSTANDARD [get_ports {MGTREFCLK0_115_P MGTREFCLK0_115_N \

MGTREFCLK1_115_P MGTREFCLK1_115_N \

MGTREFCLK0_116_P MGTREFCLK0_116_N \

MGTREFCLK1_116_P MGTREFCLK1_116_N}]

reset_property DIFF_TERM [get_ports {MGTREFCLK0_115_P MGTREFCLK0_115_N \

MGTREFCLK1_115_P MGTREFCLK1_115_N \

MGTREFCLK0_116_P MGTREFCLK0_116_N \

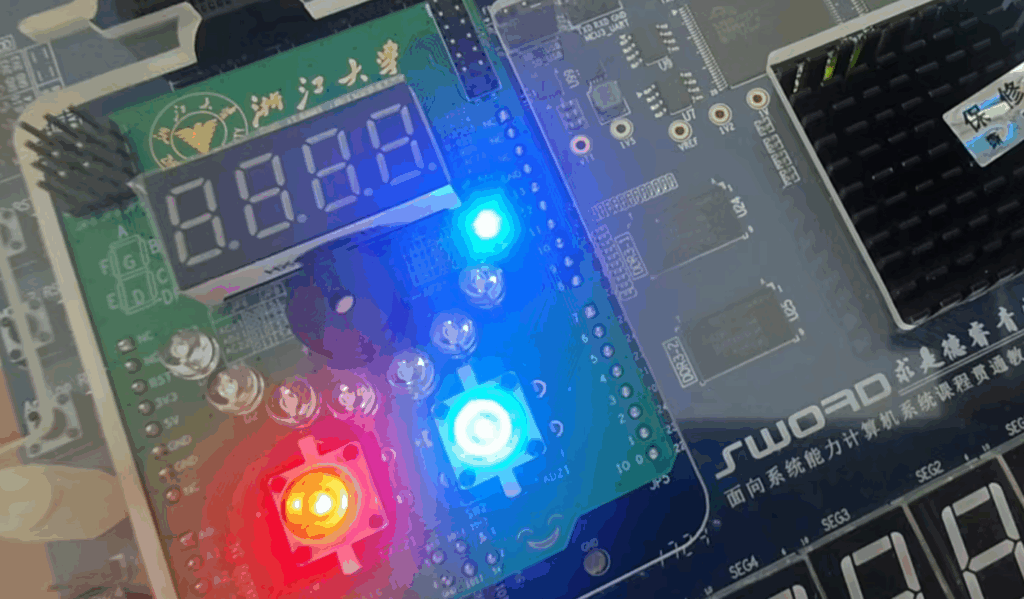

MGTREFCLK1_116_P MGTREFCLK1_116_N}]发现MGT 115_0对应的灯亮了,按秒表大概3.5秒变化一次.

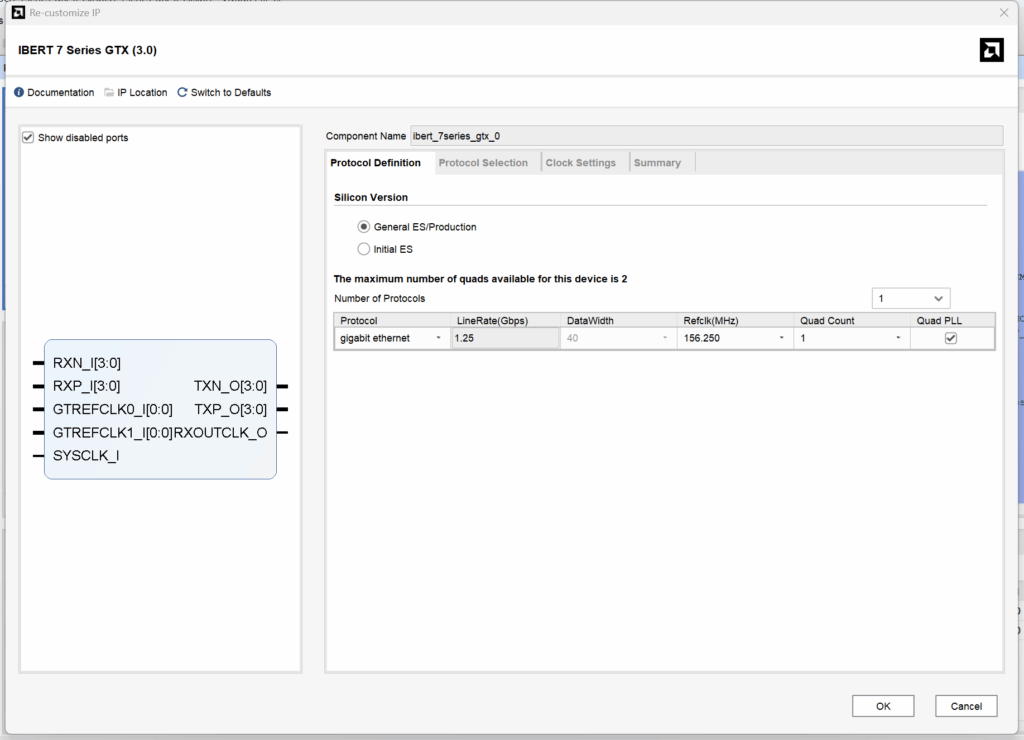

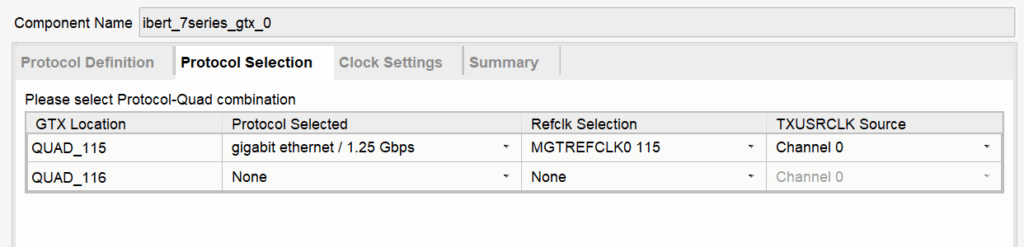

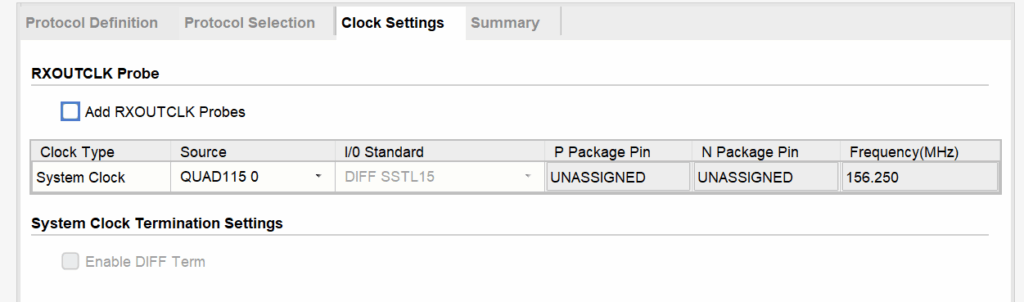

通过计算,频率接近156.250MHz,先配置,目前不知道TX_DISABLE这些,但是先写.

然后在IP右键生成示例工程,下载,接上SFP.

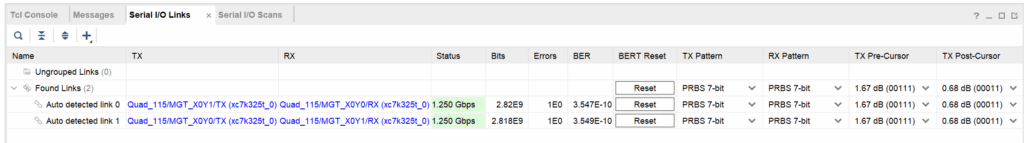

自动好了,这么严格的参数都没问题.

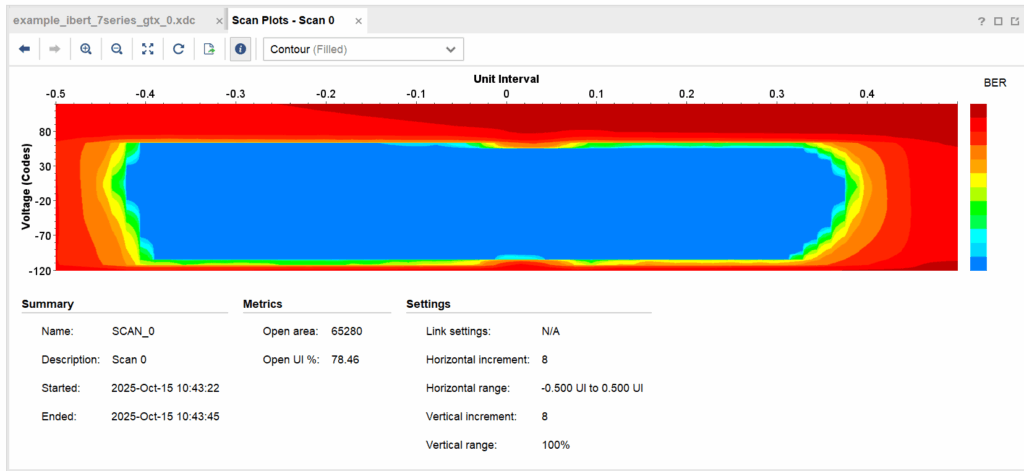

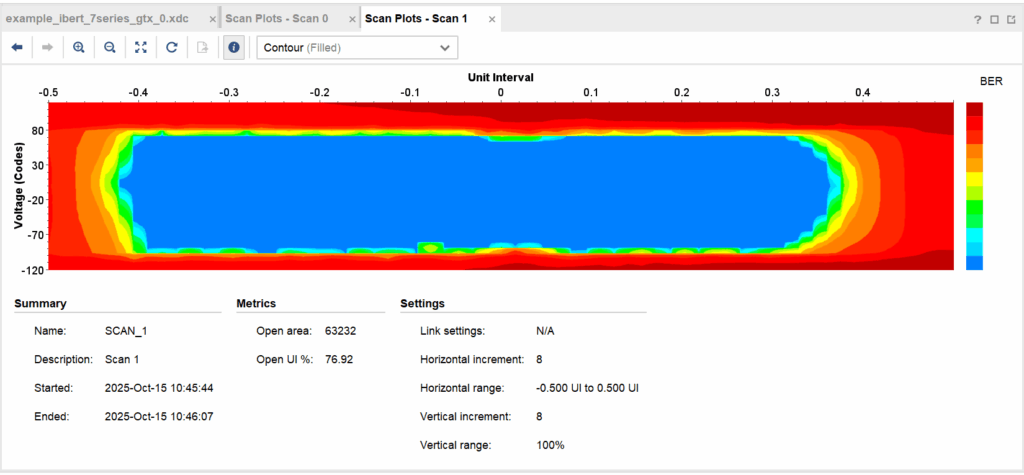

因为现在没10G模块,将就扫一下眼图.

PRBS7

PRBS31

毕竟1G低,也宽松,还可以了,10G没线测,有条件只能说自己测了.

另外这个板子上还有3个单片机,和FPGA似乎有很多走线,具体功能还不清楚.因为板子也不是我的,所以我也没测,我感觉可能时钟也是他发生的,因为我没找到高频时钟,估计是MCU的MCO吧.刚好MCU也能跑这么高频率.